![PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b832a991d759aaf18c469f02de0888c65b96a176/3-Figure6-1.png)

PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar

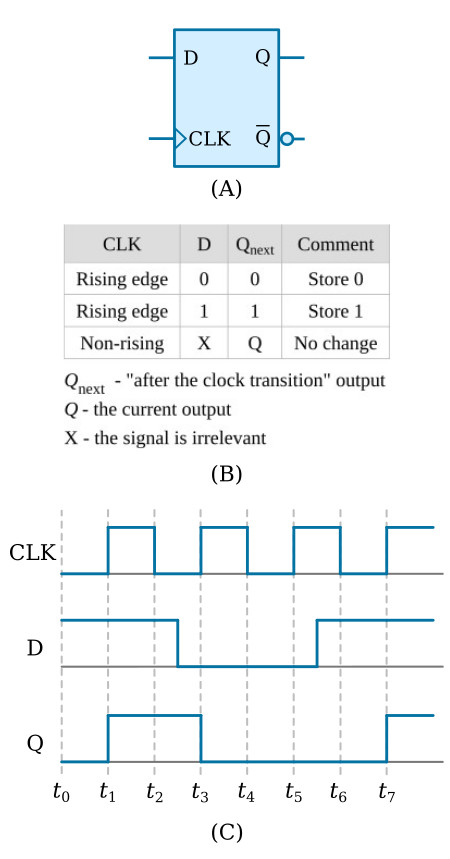

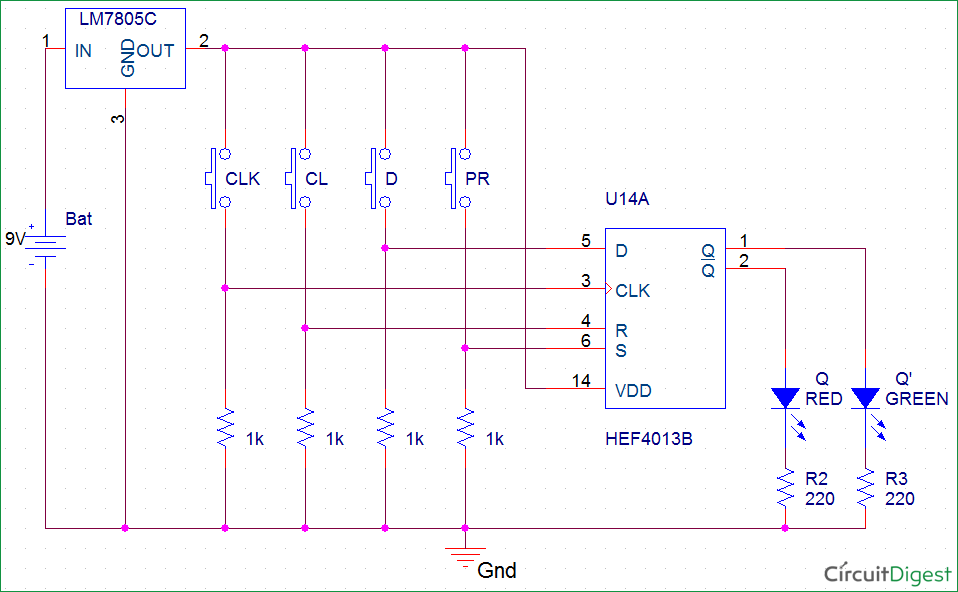

Help me calculate the device size of CML/SCL latch design and simulate the gain of it | Forum for Electronics

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

![PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b832a991d759aaf18c469f02de0888c65b96a176/4-Figure7-1.png)

PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar

PDF) Low-power high-speed performance of current-mode logic D flip-flop topology using negative-differential-resistance devices

![PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/b832a991d759aaf18c469f02de0888c65b96a176/6-Table1-1.png)

PDF] Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool | Semantic Scholar